Unità di lettura e scrittura

Load-Store Unit, LSU

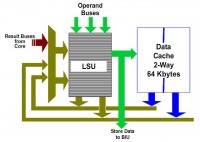

La cache L1 dati e la LSU sono mostrate in figura. La cache L1 dati supporta fino a 2 operazioni di lettura a 128 bit per ciclo oppure due scritture a 64 bit per ciclo o una mistura di queste due.

La LSU è composta di due code, LS1 di 24 elementi e LS2 di 64 elementi (12 e 32 nella precedente architettura Stars).

L’unità LS1 può iniziare due operazioni sulla cache L1 (letture oppure controllo dei tag per una successiva scrittura, ricordando che la cache usa politica di write allocate, quindi bisogna controllare se il dato è presente in cache prima di scriverlo) per ogni ciclo di clock. Può iniziare le operazioni di lettura fuori ordine, a patto che siano verificate certe condizioni.

La coda LS2 contiene le richieste che hanno dato un miss nella cache L1 dopo il controllo effettuato dalla unità LS2. Le scritture sono effettuate comunque a partire dalla coda LS2, quindi in essa andrà il risultato del check dei tag.

Le scritture a 128 bit sono trattate in modo speciale, poiché è possibile scrivere 64 bit alla volta, e occupano due posti nella LS2.

Infine la LSU si assicura che le regole di ordinamento delle operazioni in memoria della architettura x86 siano rispettate.

Write Combining

Llano ha 4 buffer da 64 byte (una linea di cache) e 8 buffer indirizzo per poter fondere fino a 8 scritture verso 4 linee diverse di cache.

Quando più scritture sono eseguite a poca distanza, può essere utile combinarle assieme prima di eseguire la scrittura completa per migliorare l’efficienza di scrittura.

Tale caratteristica è particolarmente utile quando i dati da scrivere sono verso dispositivi esterni collegati tramite il bus PCI Express o verso il south bridge.